#### **Features**

#### Architecture

- Support 1~4 multiplexing(scans)

- Support serial peripheral interface (SPI) protocol (Idle is L)

- Support dynamic frame rate: 30Hz~360Hz

- Flexible PWM control to improve visual refresh rate

- Patented S-PWM technology to improve refresh rate 20KHz

- Programmable hybrid brightness control

- Extra 2-bits high luminance mode by zone (I<sub>OUT</sub>\*100%~ I<sub>OUT</sub>\*400%)

- 8-bit adjustable global DC current setting

- Support data gray-scale:

- PWM: 12bits

- PAM: 10bits

- Hybrid: PWM-12bits/PAM-10bits

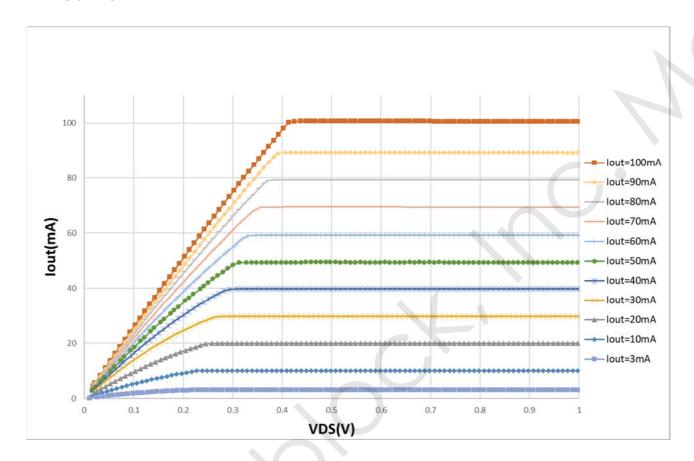

#### **Constant Current**

- 48 constant-current output channels

- Constant output current range per channel:

- 4~100mA @ 5.0V supply voltage

- Sustain voltage 24V

- Excellent output current accuracy,

- Between channels: ±3.0% (Max.) (@25mA & 100mA)

- Between chips: ±3.0% (Max.) (@25mA & 100mA)

#### **Switching Characteristics**

- Maximum data clock frequency: 15MHz @VDD=5.0V

- Maximum built-in grayscale clock frequency:70MHz

### MBI6353

#### **Protection Function**

- Compulsory LED Open/Short error detection

- Real-time LED Open/Short detection and protection

- Over temperature protection

#### Other Function

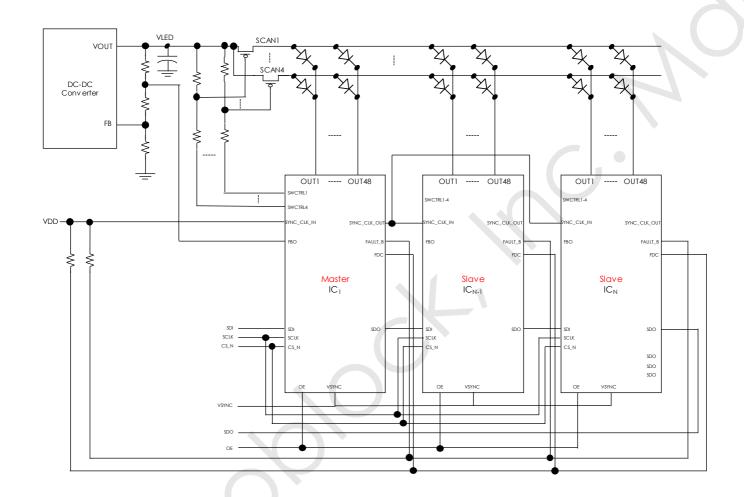

- Frame and scan synchronization for multi-IC application

- Configurable de-ghost function (lower ghost)

- Eliminate dim-line at the first scan

- VSYNC pin for vsync start pulse

- DC-DC converter feedback auto-adjustment function

- Dynamic power saving

- Dynamic black frame insertion

- Individual 3-bit output rising/falling slew rate control

- Support VRR (Variable Refresh Rate)

- Schmitt trigger input

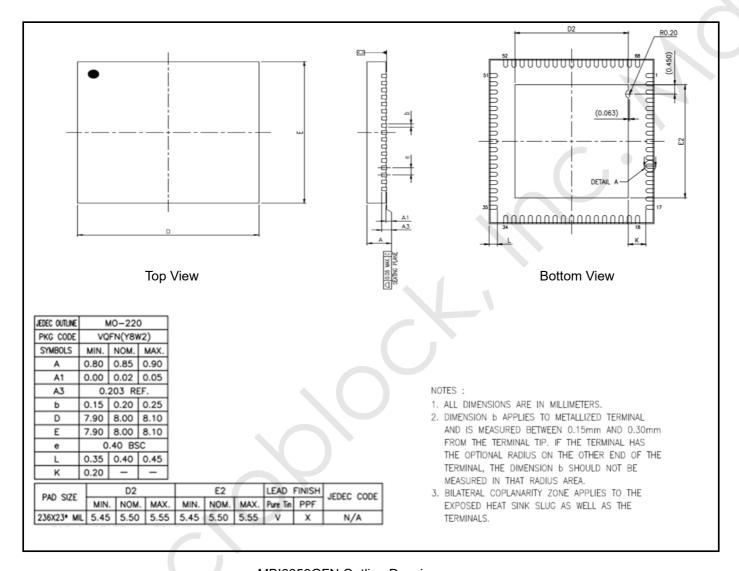

- Package: QFN68 8mm\*8mm\*0.85mm, pin pitch=0.4mm

### **Product Description**

MBI6353 is an advanced 48-channel high power constant current full-array local dimming (FALD) backlighting LED driver for large-mid LCD panel applications. The innovative architecture is designed to support up to 1:4 time-multiplexing and control up to 192 LED dimming zones application using internal Pulse Width Modulation Dimming(P-DIM) with 12-bit color depth and Analog Dimming(A-DIM) with 10-bit color depth and extra 2-bits high luminance mode by zone to improve contrast ratio for HDR applications.

Both compulsory and real-time LED error open/short detection and protection are included during both start-up and normal operation. Besides, MBI6353 also provides DC/DC feedback control, ghost elimination function and over temperature protection features.

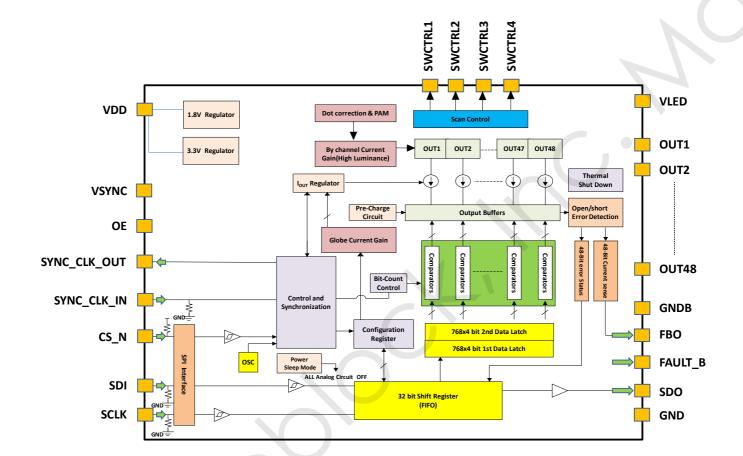

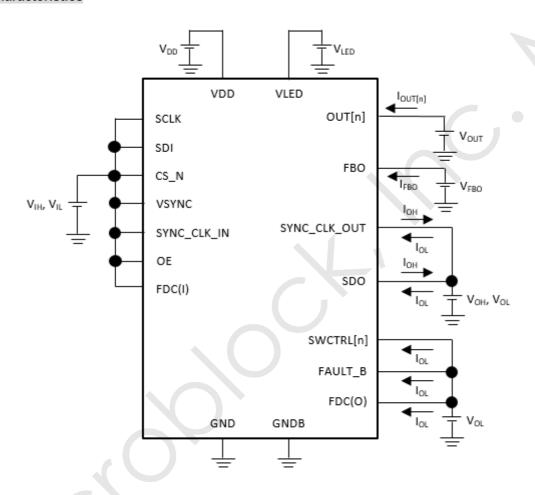

### **Block Diagram**

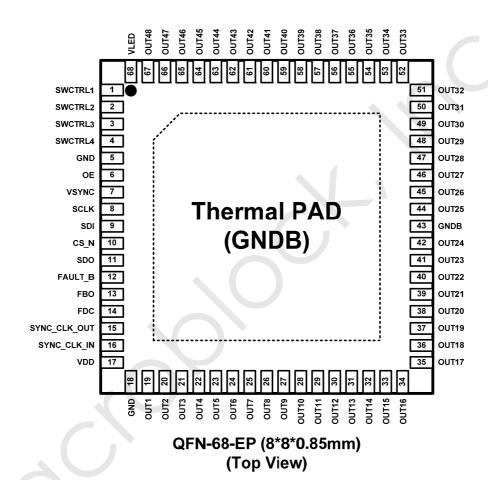

### Pin Assignment

QFN-68L-8x8x0.85-0.4

### Pin Definition

#### QFN-68L-8x8x0.85-0.4

| No.   | Name         | Туре | Description                                                                                          |

|-------|--------------|------|------------------------------------------------------------------------------------------------------|

| 1-4   | SWCTRL[1:4]  | 0    | Power switch-PMOS gate control. (open drain)                                                         |

| 5     | GND          | -    | Analog & digital ground.                                                                             |

| 6     | OE           | I    | Channel output enable                                                                                |

| 7     | VSYNC        | I    | Frame data synchronized. (pull-down resistor)                                                        |

| 8     | SCLK         | I    | Serial-data clock utilizes for shifting data. (pull-down resistor)                                   |

| 9     | SDI          | I    | Serial-data input to the shift register. (pull-down resistor)                                        |

| 10    | CS_N         | I    | Chip select. (low active) (pull-up resistor)                                                         |

| 11    | SDO          | 0    | Serial-data output from the shift register. (3.3V)                                                   |

| 12    | FAULT_B      | 0    | Real-time error status monitor. (open drain)<br>(Error status = over temperature/LED open/LED short) |

| 13    | FBO          | 0    | DC-DC Boost converter voltage feedback adjustment. (open drain)                                      |

| 14    | FDC          | I/O  | FBO function communication between ICs. (open drain)                                                 |

| 15    | SYNC_CLK_OUT | 0    | Clock synchronized to slave IC. (3.3V)                                                               |

| 16    | SYNC_CLK_IN  | I    | Clock synchronized from master IC.                                                                   |

| 17    | VDD          | -    | Power supply for analog & digital circuit.                                                           |

| 18    | GND          | -    | Analog & digital ground.                                                                             |

| 19-42 | OUT1~OUT24   | 0    | Constant current output for LED.                                                                     |

| 43    | GNDB         | -    | Constant current ground.                                                                             |

| 44~67 | OUT25~OUT48  | 0    | Constant current output for LED.                                                                     |

| 68    | VLED         | 7    | Power supply for driver-specified circuit.                                                           |

| -     | Thermal PAD  | -    | Constant current ground.<br>(The thermal pad must be soldered to ground on PCB.)                     |

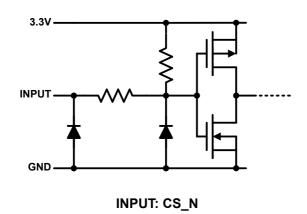

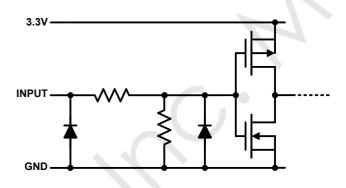

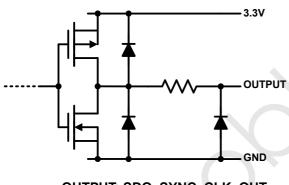

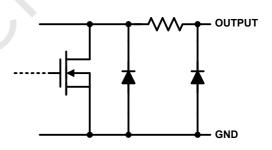

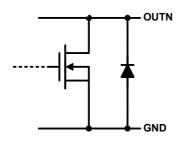

### **Equivalent Circuits of Inputs and Outputs**

INPUT: SDI, SCLK, VSYNC, OE, FDC, SYNC\_CLK\_IN

OUTPUT: SDO, SYNC\_CLK\_OUT

OUTPUT: FBO, FDC, FAULT\_B, SWCTRL1~4

**OUTPUT: OUT1~OUT48**

# Absolute Maximum Ratings

| Character                                     | ristic            | Symbol                 | Rating   | Unit |

|-----------------------------------------------|-------------------|------------------------|----------|------|

| VLED Voltage                                  |                   | V <sub>LED</sub>       | 0~26     | V    |

| Supply Voltage                                |                   | V <sub>DD</sub>        | 0~5.5    | V    |

| Input Voltage                                 |                   | V <sub>IN</sub>        | 0~5.5    | V    |

| Output Current per Outp                       | ut Channel        | I <sub>оит</sub>       | 0~100    | mA   |

| Sustaining Voltage at cu<br>(OUT1~48)         | rrent output port | V <sub>OUT[n]</sub>    | 0~26     | V    |

| Sustaining Voltage at sc<br>(SWCTRL[1:4])     | an control port   | Vswctrl[n]             | 0~26     | ٧    |

| Sustaining Voltage at op<br>(FBO/FDC/FAULT_B) | en drain port     | V <sub>FBO</sub>       | 0~5.5    | ٧    |

| Sustaining Voltage at da (SDO/SYNC_VS_OUT)    | ta output port    | V <sub>SWCTRL[n]</sub> | 0~5.5    | ٧    |

| GND Terminal Current                          |                   | I <sub>GND</sub>       | 4800     | mA   |

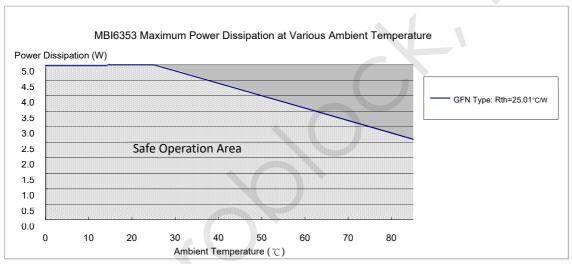

| Power Dissipation                             | QFN-68            | P <sub>D</sub>         | 5.00     | W    |

| Thermal Resistance                            | QFN-68            | R <sub>th(j-a)</sub>   | 25.01    | °C/W |

| Operating Temperature                         |                   | T <sub>opr</sub>       | -40~+85  | °C   |

| Storage Temperature                           |                   | T <sub>stg</sub>       | -55~+150 | °C   |

# **ESD Ratings**

| Characteristic              | Symbol   | Rating | Unit |

|-----------------------------|----------|--------|------|

| Human-body model (HBM)*     | VESD_HBM | ±4500  | V    |

| Charged-device model (CDM)* | VESD_CDM | ±1000  | V    |

<sup>\*</sup>JESD22-C101

### **Electrical Characteristics**

The following specifications apply for  $V_{DD}$ =5V,  $T_A$ =25°C, unless otherwise noted.

| Charact                           | teristics              | Symbol               | Condition                                                                                                                                    | Min. | Тур. | Max. | Unit  |

|-----------------------------------|------------------------|----------------------|----------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|-------|

| VLED Voltage                      |                        | V <sub>LED</sub>     | LED anodic voltage                                                                                                                           | 3.2  | -    | 24   | V     |

| Supply Voltage                    | )                      | V <sub>DD</sub>      | -                                                                                                                                            | 4.5  | 5    | 5.5  | V     |

| Start Up Voltag                   | <br>ge                 | V <sub>DD_STUP</sub> | -                                                                                                                                            | -    | 4.3  |      |       |

| UVLO Voltage                      |                        | V <sub>DD_UVLO</sub> | -                                                                                                                                            | -    | 4    | -    | \ \   |

|                                   |                        | IVLED1(ON)           | GCG1=1/1                                                                                                                                     | -    | 0.22 | -    | mA    |

|                                   |                        | I <sub>DD1(ON)</sub> | GCG2=0(Dec.)<br>(I <sub>OUT</sub> =25mA)<br> HLM=0, BC=4095(Dec.)                                                                            | -    | 9.8  | -    | mA    |

| Supply                            | Channel ON             | IVLED2(ON)           | GCG1=1/1                                                                                                                                     | -    | 0.22 | -    | mA    |

| Current                           |                        | I <sub>DD2(ON)</sub> | GCG2=255(Dec.)<br>(IOUT=100mA)<br>HLM=0, BC=4095(Dec.)                                                                                       | -    | 11.4 | -    | mA    |

|                                   | 01: 01                 | IVLED(SLPIC)         | Chip sleep enable                                                                                                                            | -    | 0.02 | -    | mA    |

|                                   | Chip Sleep             | IDD(SLPIC)           | Frame data=0                                                                                                                                 | -    | 3.2  | -    | mA    |

| l                                 | <br>ut Logic Voltage*  |                      | SDI/SCLK/VSYNC/OE                                                                                                                            | 2.42 | -    | VDD  | V     |

| Input Logic Vol                   | out Logic Voltage*     |                      | SYNC_VS_IN/CS_N                                                                                                                              | GND  | -    | 1    | V     |

| Output Logic V                    | District Lands Walkers |                      | SWCTRL[1:4]/FAULT_B<br>I <sub>OL</sub> =+2mA                                                                                                 | -    | -    | 0.2  | V     |

| Output Logic Voltage              |                        | Vон                  | SYNC_VS_OUT/SDO<br>I <sub>OH</sub> =-2mA                                                                                                     | 3.1  | -    | -    | ٧     |

| Input Pull-down Resistor          |                        | R <sub>IN_PD</sub>   | SDI/SCLK/VSYNC/OE/FDC/<br>SYNC_VS_IN                                                                                                         | -    | 580  | -    | ΚΩ    |

| Input Pull-up Resistor            |                        | R <sub>IN_PU</sub>   | CS_N                                                                                                                                         | -    | 580  | -    | ΚΩ    |

| Output Current                    |                        | Гоит                 | OUT1~OUT48=ON<br>Vout=0.3V~3.0V                                                                                                              | 4    | -    | 100  | mA    |

| Output Current                    |                        | IOUT_LEAK            | OUT1~OUT48=OFF<br>V <sub>OUT</sub> =24V                                                                                                      | -    | -    | 1    | μΑ    |

|                                   | By Channel             | dlouт_сн             | GCG1=1/8<br>GCG2=0(Dec.)<br>(IOUT=3.125mA)<br>HLM=0, BC=4095(Dec.)<br>Vout=1V                                                                | -    | -    | ±4.0 | %     |

| Current                           | by Charmer             | CHOOT_CH             | GCG1=1/1<br>GCG2=0/255(Dec.)<br>(I <sub>OUT</sub> =25mA/100mA)<br>HLM=0, BC=4095(Dec.)<br>V <sub>OUT</sub> =1V                               | -    | -    | ±3.0 | %     |

| Accuracy                          |                        | -II                  | GCG1=1/8<br>GCG2=0(Dec.)<br>(IOUT=3.125mA)<br>HLM=0, BC=4095(Dec.)<br>Vout=1V                                                                | -    | -    | ±3.0 | %     |

| By IC                             |                        | <b>dl</b> ουτ_ιc     | GCG1=1/1<br>GCG2=0/255(Dec.)<br>(IOUT=25mA/100mA)<br>HLM=0, BC=4095(Dec.)<br>V <sub>OUT</sub> =1V                                            | -    | -    | ±3.0 | %     |

| Load Regulatic<br>(Іоит vs. Vоит) | on                     | %/dVоит              | GCG1=1/1<br>GCG2=0/255(Dec.)<br>(I <sub>OUT</sub> =25mA/100mA)<br>HLM=0, BC=4095(Dec.)<br>V <sub>DD</sub> =5.0V, V <sub>OUT</sub> =0.6V/1.0V | -    | ±0.1 | ±0.6 | % / V |

| MDIOCOC                                        |                     | <b>5</b> 11101 William                                                                                                                          |   | 110 1110 | I TI PI OX |            |

|------------------------------------------------|---------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|---|----------|------------|------------|

| Line Regulation<br>(Іоит vs. V <sub>DD</sub> ) |                     | GCG1=1/1<br>GCG2=0/255(Dec.)<br>(I <sub>OUT</sub> =25mA/100mA)<br>HLM=0, BC=4095(Dec.)<br>V <sub>DD</sub> =4.5V/5V/5.5V, V <sub>OUT</sub> =1.0V | - | ±1.0     | ±2.0       | % / V      |

| Over Temperature Protection                    | $T_{SD}$            | Thermal shutdown threshold                                                                                                                      | - | 150      | -          | $^{\circ}$ |

| Over Temperature Protection                    | T <sub>SD_HYS</sub> | Recovery hysteresis                                                                                                                             | - | 30       | -          | $^{\circ}$ |

<sup>\*</sup>There is a LDO to convert VDD to 3.3V for internal operation, so VIH and VIL are all based on the internal 3.3V.

MBI6353

- 10 -

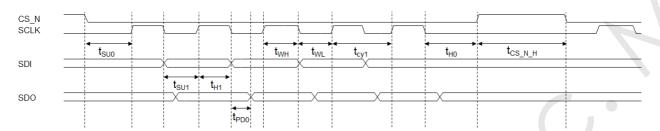

### **Switching Characteristics**

The following specifications apply for V<sub>DD</sub>=5V, T<sub>A</sub>=25°C, unless otherwise noted.

| Chara                   | cteristics                                     | Symbol           | Condition                                                              | Min.  | Тур.  | Max. | Unit |

|-------------------------|------------------------------------------------|------------------|------------------------------------------------------------------------|-------|-------|------|------|

| Cycle time              | SCLK clock period                              | t <sub>CY1</sub> |                                                                        |       | 66.67 |      | ns   |

| Data setup Time         | CS_N setup time relative to the rise of SCLK   | t <sub>SU0</sub> |                                                                        | 33.33 | -     | -    | ns   |

| ·                       | SDI setup time relative to the rise of SCLK    | tsu1             |                                                                        | 8     | -     | -    | ns   |

|                         | CS_N hold time relative to the rise of SCLK    | t <sub>H0</sub>  |                                                                        | 33.33 | -     | . 0  | ns   |

| Data hold Time          | SDI setup time relative to the rise of SCLK    | t <sub>H1</sub>  | IOUT=25mA<br>V <sub>LED</sub> =24V                                     | 8     |       | -    | ns   |

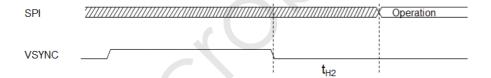

|                         | SPI operation relative to the fall of VSYNC    | t <sub>H2</sub>  | V <sub>LOAD</sub> =5V<br>R <sub>L</sub> =160Ω                          | 2     | -     | -    | μs   |

|                         | High period pulse width of SCLK                |                  | C <sub>L</sub> =100pF<br>C <sub>1</sub> =10uF                          | 33.33 | -     | -    | ns   |

| Pulse Width             | Low period pulse width of SCLK                 | twL              | C <sub>2</sub> =0.1µF<br>C <sub>3</sub> =10uF<br>C <sub>4</sub> =0.1µF | 33.33 | -     | -    | ns   |

| Puise Width             | High period pulse width of CS_N                | tcs_n_h          | C <sub>5</sub> =10μF<br>C <sub>6</sub> =0.1μF                          | 2     | -     | -    | μs   |

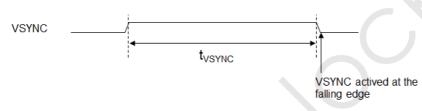

|                         | High pulse width of VSYNC                      | tvsync           | C <sub>SDO</sub> =50pF                                                 | 1     | -     | -    | μs   |

| Compulsory error detec  | ction operation time /1scan                    | terr-c           |                                                                        | 10    | _     | -    | us   |

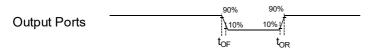

| Output Rise Time of Ou  | utput Rise Time of Output Ports(Highest Speed) |                  |                                                                        |       | 100   |      | ns   |

| Output Fall Time of Out | tofн                                           |                  |                                                                        | 100   |       | ns   |      |

| Output Rise Time of Ou  | torl                                           |                  |                                                                        | 520   |       | ns   |      |

| Output Fall Time of Out | put Ports(Lowest Speed)                        | tofl             |                                                                        |       | 210   |      | ns   |

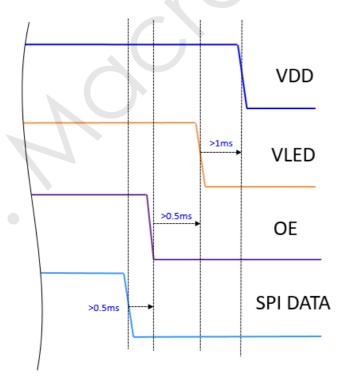

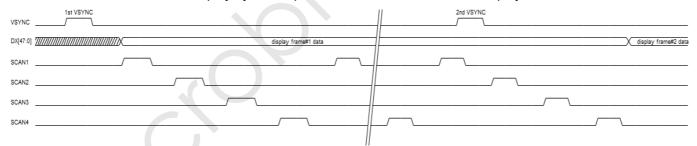

### Timing waveform

(1)

(2)

(3)

(4)

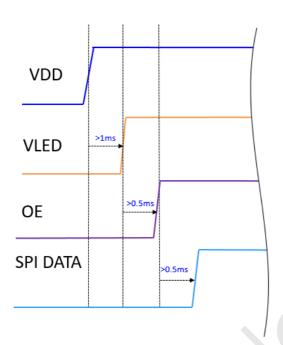

Recommend power-on sequence

#### POWER UP

#### POWER DOWN

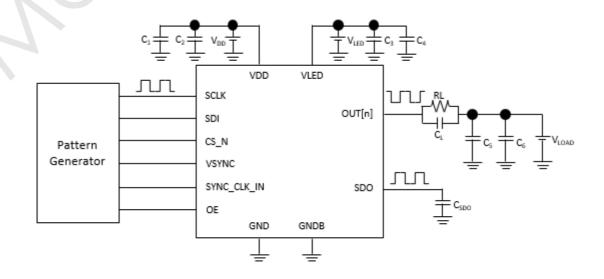

Test Circuit for Electrical/Switching Characteristics

#### **Electrical Characteristics**

#### **Switching Characteristics**

### System application

### **Output Current Setting**

#### Global output current

The global output current is set by the two configuration registers.

Global output current can be adjusted by "ADDRESS: 0x0, bit 11 ~ bit 10" and "ADDRESS: 0x4, bit 15 ~ bit 8"

|    | SPI ADDRESS:0x0 |    |    |    |    |   |   |   |   |   |   |   |   |   |   |

|----|-----------------|----|----|----|----|---|---|---|---|---|---|---|---|---|---|

| 15 | 14              | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| 0  | 0               | 0  | 0  | 1  | 1  | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 |

| Bit   | Attribute  | Definition                           | Default<br>Value | Function                                                                                    |

|-------|------------|--------------------------------------|------------------|---------------------------------------------------------------------------------------------|

| 11:10 | Read/Write | Global current<br>division<br>(GCG1) |                  | Mode change for output current lout 00: Mode= 1/8 01: Mode= 1/4 10: Mode= 1/2 11: Mode= 1/1 |

|                 |                                                                    |  |  |  |  | SP | I ADDF | RESS: | 0x4 |  |  |  |  |  |  |

|-----------------|--------------------------------------------------------------------|--|--|--|--|----|--------|-------|-----|--|--|--|--|--|--|

| 15              | 5   14   13   12   11   10   9   8   7   6   5   4   3   2   1   0 |  |  |  |  |    |        |       |     |  |  |  |  |  |  |

| GC <sub>7</sub> | C7 GC6 GC5 GC4 GC3 GC2 GC1 GC0                                     |  |  |  |  |    |        |       |     |  |  |  |  |  |  |

| Bit  | Attribute  | Definition                       | Default<br>Value | Function                                                                                                               |

|------|------------|----------------------------------|------------------|------------------------------------------------------------------------------------------------------------------------|

| 15:8 | Read/Write | Global current setting<br>(GCG2) | 00000000         | At GCG1=1(Default):<br>8'b00000000 = 25mA<br>8'b00000001 = 25.29mA<br><br>8'b10011001 =70mA<br><br>8'b11111111 = 100mA |

#### Formula for default setting:

$$I_{OUT} = \left[25 + \left(\frac{GCG2}{255} \times 75\right)\right] \times GCG1 \text{ (Unit: mA)}$$

$$GCG2 = \sum_{n=0}^{7} (GC_n \cdot 2^n) = 0 \sim 255$$

#### Example:

1. GCG1=1/4, GCG2 = 0(default),

$$I_{OUT} = \left[25 + \left(\frac{0}{255} \times 75\right)\right] \times \frac{1}{4} = 6.25 \text{mA}$$

2. GCG1=1/2, GCG2 = 85,

$$I_{OUT} = \left[25 + \left(\frac{85}{255} \times 75\right)\right] \times \frac{1}{2} = 25 \text{mA}$$

3. GCG1=1(default), GCG2 = 85,

$$I_{OUT} = \left[25 + \left(\frac{85}{255} \times 75\right)\right] \times 1 = 50 \text{mA}$$

2. GCG1=1/2, GCG2 = 85,

$$I_{OUT} = \left[25 + \left(\frac{85}{255} \times 75\right)\right] \times \frac{1}{2} = 25 \text{mA}$$

3. GCG1=1(default), GCG2 = 85,  $I_{OUT} = \left[25 + \left(\frac{85}{255} \times 75\right)\right] \times 1 = 50 \text{mA}$

4. GCG1=1(default), GCG2 = 153,  $I_{OUT} = \left[25 + \left(\frac{153}{255} \times 75\right)\right] \times 1 = 70 \text{mA}$

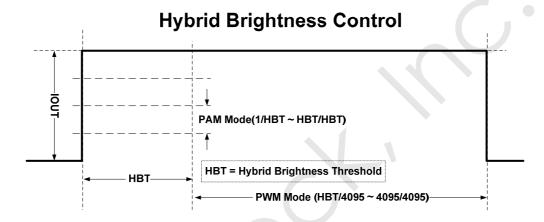

### Brightness control

#### Hybrid mode:

There is brightness control with hybrid (PWM/PAM) mode applications in this chip. Configuration register can set brightness mode-change point which is threshold of brightness mode. The brightness code is greater than the threshold using PWM mode, and less than the threshold using PAM mode.

Hybrid mode and PWM only mode are 12-bit brightness control, but PAM only mode is just 10-bit brightness control.

Hybrid (PWM/PAM) brightness threshold can be adjusted by ADDRESS: 0x0, bit 3 ~ bit 0.

|    | SPI ADDRESS:0x0                                                    |  |  |  |  |  |  |  |  |  |

|----|--------------------------------------------------------------------|--|--|--|--|--|--|--|--|--|

| 15 | 5   14   13   12   11   10   9   8   7   6   5   4   3   2   1   0 |  |  |  |  |  |  |  |  |  |

| -  | P P P                                                              |  |  |  |  |  |  |  |  |  |

| Bit | Attribute  | Definition                              | Default<br>Value | Function                                                                                                                                                                                             |

|-----|------------|-----------------------------------------|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3:0 | Read/Write | Hybrid(PWM/PAM)<br>brightness threshold | 0000             | 0000: PWM only mode 0001: 4 0010: 8 0011: 16 0100: 32 0101: 64 0110: 128 0111: 256 1000: 512 1001: 1024 1010 ~ 1110: not used(same as code '0000') 1111: PAM only mode (10-bit brightness code only) |

#### High luminance mode:

LED brightness control can be achieved by configuration register of brightness control settings. Brightness code can be adjusted by ADDRESS: 0x20~0x4F/0x50~0x7F, 0x80~0xAF/0xB0~0xDF, bit 11 ~ bit 0. High luminance mode can be adjusted by ADDRESS: 0x20~0x4F/0x50~0x7F, 0x80~0xAF/0xB0~0xDF, bit 13 ~ bit 12.

|    | SPI ADDRESS:0x20~0x4F, 0x50~0x7F, 0x80~0xAF, 0xB0~0xDF |                 |     |                  |                  |                 |                 |                 |                 |                 |                 |                 |                 |                 |                 |

|----|--------------------------------------------------------|-----------------|-----|------------------|------------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|

| 15 | 14                                                     | 13              | 12  | 11               | 10               | 9               | 8               | 7               | 6               | 5               | 4               | 3               | 2               | 1               | 0               |

| -  | -                                                      | HL <sub>1</sub> | HL₀ | BC <sub>11</sub> | BC <sub>10</sub> | BC <sub>9</sub> | BC <sub>8</sub> | BC <sub>7</sub> | BC <sub>6</sub> | BC <sub>5</sub> | BC <sub>4</sub> | BC <sub>3</sub> | BC <sub>2</sub> | BC <sub>1</sub> | BC <sub>0</sub> |

#### Note:

The register address 0x20~0x4F for SCAN1 Brightness code of Channel48~Channel1 Register The register address 0x50~0x7F for SCAN2 Brightness code of Channel48~Channel1 Register The register address 0x80~0xAF for SCAN3 Brightness code of Channel48~Channel1 Register The register address 0x80~0xDF for SCAN4 Brightness code of Channel48~Channel1 Register

#### Formula for default setting:

$$I_{LED\_HYBRID} = [I_{OUT} \times (HLM + 1)] \times \frac{BC\_HYB\_PWM}{HBT} \times \frac{HBT}{4095}$$

(Unit: mA)

$$I_{LED\_PWM\_only} = [I_{OUT} \times (HLM + 1)] \times \frac{BC\_HYB\_PWM}{4095}$$

(Unit: mA)

$$I_{LED\_PAM\_only} = \left[I_{OUT} \times (HLM + 1)\right] \times \frac{BC\_PAM + 1}{1024} \text{ (Unit: mA)(Note: } I_{LED\_PAM\_only} = 0 \text{ when BC\_PAM} = 0)$$

$$\left[ \text{BC\_HYB\_PMW} = \sum_{n=0}^{11} (\text{BC}_n \cdot 2^n) = 0 {\sim} 4095 \right]$$

$$\left[ BC_{-}PAM = \sum_{n=0}^{9} (BC_{n} \cdot 2^{n}) = 0 \sim 1023 \right]$$

$$\left[ HLM = \sum_{n=0}^{2} (HL_n \cdot 2^n) = 0 \sim 3 \right]$$

### Digital function

#### ■ Control interface

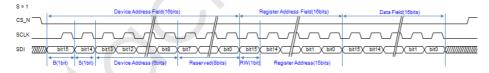

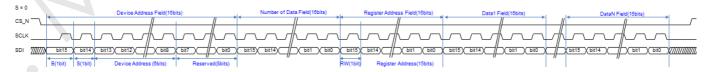

MBI6353 supports 4-wire SPI interface to communicate with the controller. The communication starts at the CS\_N transition from High to Low. Data present at Serial Data Input (SDI) is latched on the rising edge of Serial Clock (SCLK). The protocol consists of 16-bit device address, 16-bit number of data, 16-bit register address and 16-bit data. (Only support SPI mode: CPHA=0 and CPOL=0)

16-bit Device Address

| Bit  | Definition | Value       | Function                                                                                                                                                                                         |

|------|------------|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15   | В          | 1'b0        | Broadcast 1: Message to all device (only write command) 0: Message to single device                                                                                                              |

| 14   | S          | 1'b0        | Single data 1: Single data transmission (only one word (16 bits) 0: Burst transmission with number of data which is defined by NrOfdata[15:0]                                                    |

| 13:8 | DevAddr    | 6'h00~6'h3F | Device Address 0x00: Write/read same data to same register of all devices (B=1) 0x01 to 0x3E: Device address for device 1 to 62 0x3F: Write different data to same register of all devices (B=1) |

| 7:0  | Reserved   | 7'h00       |                                                                                                                                                                                                  |

#### 16-bit Number of Data

| Bit  | Definition | Value             | Function                |

|------|------------|-------------------|-------------------------|

| 15:0 | NrOfdata   | 16'h0000~16'hffff | Number of data in frame |

#### 16-bit Register Address

| Bit  | Definition | Value             | Function                                                 |

|------|------------|-------------------|----------------------------------------------------------|

| 15   | RW         | 1.00              | Read from register address     Write to register address |

| 14:0 | RegAddr    | 15'h0000~15'h7FFF | Register Address                                         |

#### 16-bit Data

| Bit  | Definition | Value             | Function |

|------|------------|-------------------|----------|

| 15:0 | Data       | 16'h0000~16'hffff | Data     |

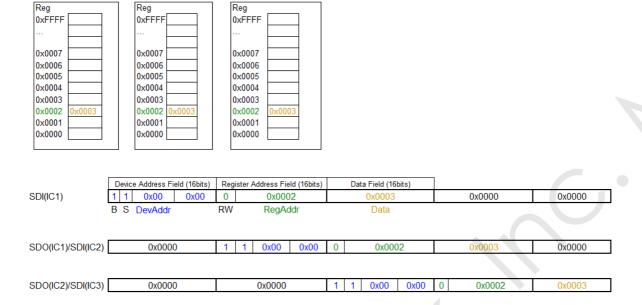

#### The single data bit (S) of 16-bit device address is "1"

#### The single data bit (S) of 16-bit device address is "0" (burst mode)

#### Write operation

To active the write operation, set the R/W bit to "0". If the register address of header is set to "N", the 16-bit data will be written to the register address is "N"

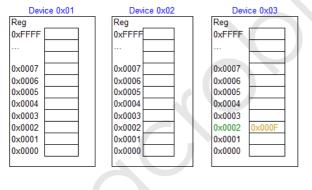

Write single data to device1 when the broadcast bit (B) is set to "0" and single data bit (S) is set to "1".

Write single data to device3 when the broadcast bit (B) is set to "0" and single data bit (S) is set to "1".

|                   | Device Address Field (16bits) | Reg | ister /   | Address Fie | ld (16bits) | Data Field (16bits) |   |       |      |        |                                                |        |

|-------------------|-------------------------------|-----|-----------|-------------|-------------|---------------------|---|-------|------|--------|------------------------------------------------|--------|

| SDI(IC1)          | SDI(IC1) 0 1 0x03 0x00        |     | 0 0x0002  |             | 0x000F      |                     |   |       |      | 0x0000 | 0x0000                                         |        |

|                   | B S DevAddr                   | RW  | V RegAddr |             | Data        |                     |   |       |      | •      | <u>.                                      </u> |        |

|                   |                               |     |           |             |             |                     |   |       |      |        |                                                |        |

| SDO(IC1)/SDI(IC2) | 0x0000                        | 0   | 1         | 0x03        | 0x00        | 0                   |   | 0x000 | 2    |        | 0x000F                                         | 0x0000 |

|                   |                               |     |           |             |             |                     |   |       |      |        |                                                |        |

| SDO(IC2)/SDI(IC3) | 0x0000                        |     |           | 0x0000      |             | 0                   | 1 | 0x03  | 0x00 | 0      | 0x0002                                         | 0x000F |

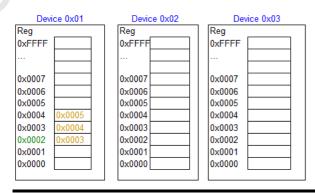

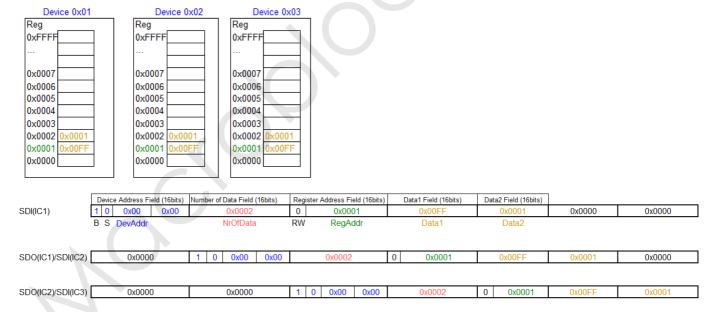

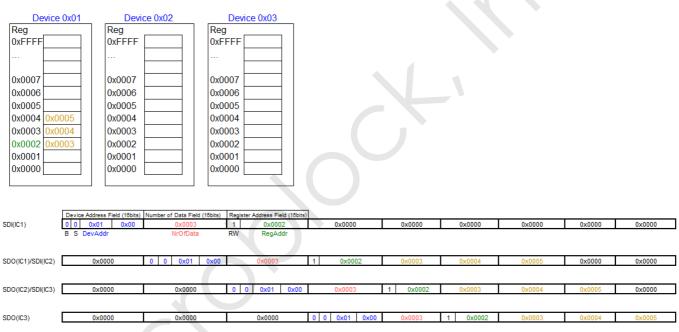

Write multiple data to device1 when the broadcast bit (B) and single data bit (S) are set to "0".

### 48-Channel Low Voltage High Constant Current LED Driver with 1:4 Time-Multiplexing

|                   | Device Address Field (16bits) | Number of Data Field (16bits) | Register Address Field (16bits) | Data1 Field (16bits) | Data2 Field (16bits) | Data3 Field (16bits) |        |        |

|-------------------|-------------------------------|-------------------------------|---------------------------------|----------------------|----------------------|----------------------|--------|--------|

| SDI(IC1)          | 0 0 0x01 0x00                 | 0x0003                        | 0 0x0002                        | 0x0003               | 0x0004               | 0x0005               | 0x0000 | 0x0000 |

|                   | B S DevAddr                   | NrOfData                      | RW RegAddr                      | Data1                | Data2                | Data3                |        |        |

|                   |                               |                               |                                 |                      |                      |                      |        |        |

|                   |                               |                               |                                 |                      |                      |                      |        |        |

| SDO(IC1)/SDI(IC2) | 0x0000                        | 0 0 0x01 0x00                 | 0x0003                          | 0 0x0002             | 0x0003               | 0x0004               | 0x0005 | 0x0000 |

|                   |                               |                               |                                 |                      |                      |                      |        |        |

|                   |                               |                               |                                 |                      |                      |                      |        |        |

| SDO(IC2)/SDI(IC3) | 0x0000                        | 0x0000                        | 0 0 0x01 0x00                   | 0x0003               | 0 0x0002             | 0x0003               | 0x0004 | 0x0005 |

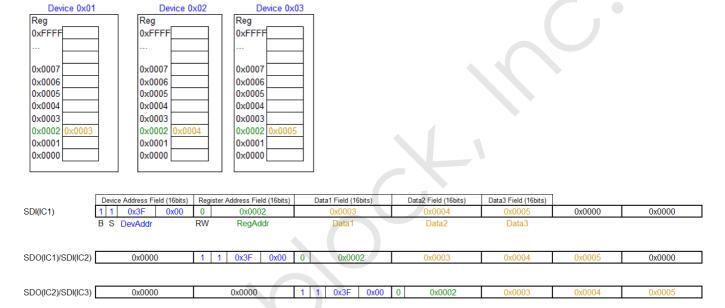

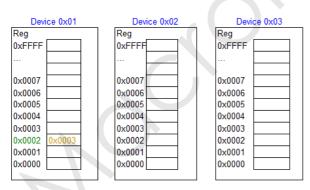

Write different single data to same register address of all device when the broadcast bit (B) and single data bit (S) are set to "1" and the DevAddr bits of 16-bit device address are set to "0x3F".

Write different multiple data to all device when the broadcast bit (B) is set to "1", single data bit (S) is set to "0" and the DevAddr bits of 16-bit device address are set to "0x3F".

Write same single data to same register address of all device when the broadcast bit (B) and single data bit (S) are set to "1" and the DevAddr bits of 16-bit device address are set to "0x00".

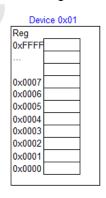

Device 0x02

### 48-Channel Low Voltage High Constant Current LED Driver with 1:4 Time-Multiplexing

Device 0x03

Write multiple same data to same register address of all device when the broadcast bit (B) is set to "1", single data bit (S) is set to "0" and the DevAddr bits of 16-bit device address are set to "0x00".

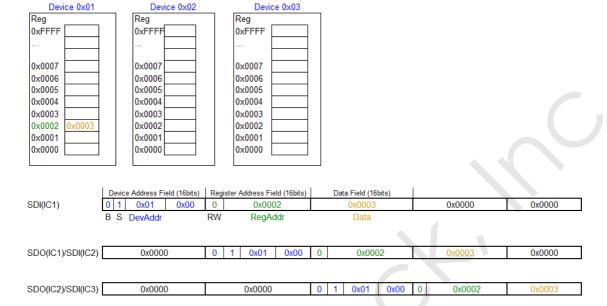

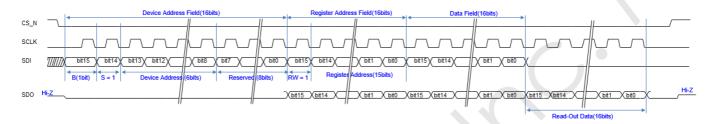

#### Read operation

To active the read operation, set the R/W bit to "1". If the register address bit is set to "N", the 16-bit data of register address is "N" will be output by SDO. MBI6353 changes SDO state from high-impedance to output and drives read-out data at the falling edge of SCLK. The read data are transmitted MSB first. After finishing read-out transmission, SDO becomes high-impedance state when CS becomes high. At the read operation, the broadcast (B) bit must keep "0".

Read single data from device1 when the broadcast bit (B) is set to "0" and single data bit (S) is set to "1".

| SDI(IC1)          | Device Address Field (16bits)   0   1   0x01   0x00 | Register Address Field (16bits)  1 0x0002 |         |   | 0x0000 |      |   | 0x0000     | <u> </u> | 0x0000 | 0x0000 |

|-------------------|-----------------------------------------------------|-------------------------------------------|---------|---|--------|------|---|------------|----------|--------|--------|

|                   | B S DevAddr                                         | RW R                                      | egAddr  |   |        |      |   |            | ·        |        |        |

| SDO(IC1)/SDI(IC2) | 0x0000                                              | 0 1 0x                                    | 01 0x00 | 0 | 0x000  | 2    |   | 0x0003     |          | 0x0000 | 0x0000 |

|                   |                                                     |                                           |         |   |        |      |   |            |          |        |        |

| SDO(IC2)/SDI(IC3) | 0x0000                                              | 0x0                                       | 000     | 0 | 1 0x01 | 0x00 | 0 | 0x0002     |          | 0x0003 | 0x0000 |

|                   |                                                     |                                           |         |   |        |      |   |            |          |        |        |

| SDO(IC3)          | 0x0000                                              | 0x0                                       | 000     |   | 0x0000 |      | 0 | 1 0x01 0x0 | 0 0      | 0x0002 | 0x0003 |

Dummy number(send "0" to SDI(IC1)=(IC number+data number)x16 bits

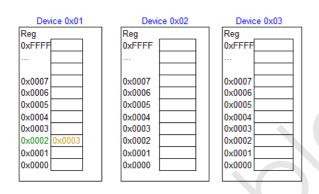

Read single data from device3 when the broadcast bit (B) is set to "0" and single data bit (S) is set to "1".

| De     | vice 0x03 |

|--------|-----------|

| Reg    |           |

| 0xFFFF |           |

|        |           |

|        |           |

| 0x0007 |           |

| 0x0006 |           |

| 0x0005 |           |

| 0x0004 |           |

| 0x0003 |           |

| 0x0002 | 0x000F    |

| 0x0001 |           |

| 0x0000 |           |

|        |           |

### 48-Channel Low Voltage High Constant Current LED Driver with 1:4 Time-Multiplexing

|                   | Device Address Fie | eld (16bits) | Regist   | er Address Fiel | ld (16bits) |        |        |      |   |        |      |   |        |        |  |

|-------------------|--------------------|--------------|----------|-----------------|-------------|--------|--------|------|---|--------|------|---|--------|--------|--|

| SDI(IC1)          | 0 1 0x03 0x00      |              | 1 0x0002 |                 |             | 0x0000 |        |      |   | 0x0000 |      |   | 0x0000 | 0x0000 |  |

|                   | B S DevAddr        |              | RW       | RegAd           | ldr         |        |        |      |   |        |      |   |        |        |  |

|                   |                    |              |          |                 |             |        |        |      |   |        |      |   |        |        |  |

|                   |                    |              |          |                 |             |        |        |      | _ |        |      |   |        |        |  |

| SDO(IC1)/SDI(IC2) | 0x0000             | )            | 0        | 1 0x03          | 0x00        | 1      | 0x000  | 2    |   | 0x0000 |      |   | 0x0000 | 0x0000 |  |

|                   |                    |              |          |                 |             |        |        |      |   |        |      |   |        |        |  |

|                   |                    |              |          |                 |             |        |        |      |   |        |      |   |        |        |  |

| SDO(IC2)/SDI(IC3) | 0x0000             | )            |          | 0x0000          |             | 0      | 1 0x03 | 0x00 | 1 | 0x000  | 2    |   | 0x0000 | 0x0000 |  |

|                   |                    |              |          |                 |             |        |        |      |   |        |      |   |        |        |  |

| SDO(IC3)          | 0x0000             | )            |          | 0x0000          |             |        | 0x0000 |      | 0 | 1 0x03 | 0x00 | 1 | 0x0002 | 0x000F |  |

Dummy number(send "0" to SDI(IC1)=(IC number+data number)x16 bits

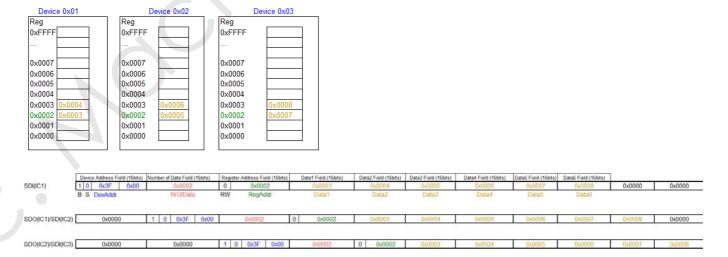

Read multiple data from device1 when the broadcast bit (B) is set to "0" and single data bit (S) is set to "0".

Dummy number(send "0" to SDI(IC1)=(IC number+data number)x16 bits

#### ■ SPI Transfer Checksum

MBI6353 supports the interface checksum verification mode. When checksum verification mode is enabled by the bit "checksum" in register 0x01 (bit 0) is set to "1", the Host controller will add the calculated 16-bit checksum result at the end of SPI transmission.

If the sum of the register address, all data and checksum is zero the transfer is considered as correct. Otherwise the transfer has no effect and the "checksum fault" bit (Reg. 0x03FF, bit 3) is set until the next valid data transfer.

#### Checksum calculation Examples:

|          | Device Address Field (16bits) Number of Data Field (16bits) |   |         |      |          | Regis | ter Address Field (16bits) | Data1 Field (16bits) | Data2 Field (16bits) | Data3 Field (16bits) | Checksum Field (16bits) |

|----------|-------------------------------------------------------------|---|---------|------|----------|-------|----------------------------|----------------------|----------------------|----------------------|-------------------------|

| SDI(IC1) | 0                                                           | 0 | 0x01    | 0x00 | 0x0003   | 0     | 0x0002                     | 0x0003               | 0x0004               | 0x0005               | 0xFFF2                  |

|          | В                                                           | S | DevAddr |      | NrOfData | RW    | RegAddr                    | Data1                | Data2                | Data3                | Checksum                |

0002h+0003h+0004h+0005h+FFF2h = 0000h -> checksum result correct

#### Write operation with checksum enable

|                   | D | evice | Address Field | (16bits) | Regis | ster Address Field (16bits) | Data Field (16bits) | CheckSum Field (16bits) |        |        |

|-------------------|---|-------|---------------|----------|-------|-----------------------------|---------------------|-------------------------|--------|--------|

| SDI(IC1)          | 0 | 1     | 0x01          | 0x00     | 0     | 0x0002                      | 0x0003              | 0xFFFB                  | 0x0000 | 0x0000 |

|                   | В | S     | DevAddr       |          | RW    | RegAddr                     | Data                | Checksum                |        |        |

|                   |   |       |               |          |       |                             |                     |                         |        |        |

| SDO(IC1)/SDI(IC2) |   |       | 0x0000        |          | 0     | 1 0x01 0x00                 | 0 0x0002            | 0x0003                  | 0xFFFB | 0x0000 |

|                   |   |       |               |          |       |                             |                     |                         |        |        |

| SDO(IC2)/SDI(IC3) |   |       | 0x0000        |          |       | 0x0000                      | 0 1 0x01 0x00       | 0 0x0002                | 0x0003 | 0xFFFB |

#### Read operation with checksum enable

|                   | D | evice | Address Field | (16bits) | Regis | ter A | ddress Fie | eld (16bits) |   | Check | Sum Field | (16bits) |     |        |      |   |        |    |       |   |        |

|-------------------|---|-------|---------------|----------|-------|-------|------------|--------------|---|-------|-----------|----------|-----|--------|------|---|--------|----|-------|---|--------|

| SDI(IC1)          | 0 | 1     | 0x01          | 0x00     | 1     |       | 0x000      | 02           |   |       | 0x7FFE    |          |     | 0x0000 | 0    |   | 0x0000 | 0) | (0000 |   | 0x0000 |

| •                 | В | S     | DevAddr       |          | RW    |       | RegA       | ddr          |   | (     | Checksu   | m        |     |        |      |   |        |    |       |   |        |

|                   |   |       |               |          |       |       |            |              |   |       |           |          |     |        |      |   |        |    |       |   |        |

| SDO(IC1)/SDI(IC2) |   |       | 0x0000        |          | 0     | 1     | 0x01       | 0x00         | 0 |       | 0x000     | )2       |     | 0x0003 | 3    |   | 0x7FFE | 0) | (0000 |   | 0x0000 |

|                   |   |       |               |          |       |       |            |              |   |       |           |          |     |        |      |   |        |    |       |   | _      |

|                   | _ |       |               |          |       |       |            |              |   |       |           |          | 1-1 |        |      |   |        | _  |       | _ |        |

| SDO(IC2)/SDI(IC3) |   |       | 0x0000        |          |       |       | 0x0000     |              | 0 | 1     | 0x01      | 0x00     | 0   | 0x00   | 02   |   | 0x0003 | Ox | 7FFE  |   | 0x0000 |

|                   |   |       |               |          |       |       |            |              |   |       |           |          |     |        |      |   |        |    |       |   |        |

| SDO(IC3)          |   |       | 0x0000        |          |       |       | 0x0000     |              |   |       | 0x0000    | 1        | 0 1 | 0x01   | 0x00 | 0 | 0x0002 | 0) | (0003 |   | 0x7FFE |

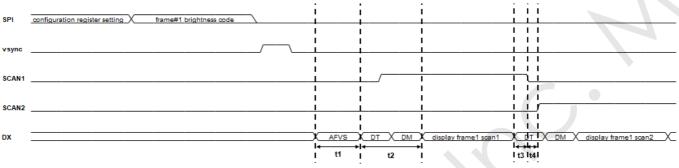

#### **Initialization Sequence**

At initialization, users program the configuration register. Then, the send the brightness code register (48 channels x 4 scan lines) and active the "VSYNC" pin. The brightness code will be updated and display by the output channels after the "VSYNC" active.

t1: after vsync period

t2: dead time period(configuration4 register bit[7:0]) + dummy time period(configuration4 register bit[15:8]) GCLK cycles t3: scan change period(configuration8 register bit[7:0]) GCLK cycles

t4: MOS separate period(configuration8 register bit[15:8]) GCLK cycles

#### Frame data update

The frame1 data will be display by the output channels after the 1st VSYNC active. When the 2nd VSYNC active, the frame2 data will be display by the output channels until the last scan display of the frame1 data is done.

#### ■ Register Lock/Unlock

All registers can be locked to prevent noise from causing the register to be miswritten. Check the status of register lock or unlock by register 0x3FF bit 4.

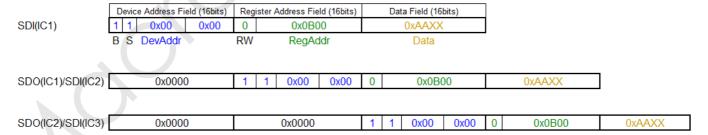

To unlock write configuration 1~16 (register 0x0~0xF) and channel mask code (register 0x401~0x403) register operation, write data 0xCCXX to register 0x0B00.

|                   | Device Address Field (16bits) |         |      |    | ister / | Address Fie | ld (16bits) |        | Dat | a Field (16h | oits) |   |        |   |        |

|-------------------|-------------------------------|---------|------|----|---------|-------------|-------------|--------|-----|--------------|-------|---|--------|---|--------|

| SDI(IC1)          | 1 1                           | 0x00    | 0x00 | 0  | 0x0B00  |             |             | 0xCCXX |     |              |       |   |        |   |        |

|                   | B S                           | DevAddr |      | RW |         | RegAc       | ldr         |        |     | Data         |       |   |        |   |        |

|                   |                               |         |      |    |         |             |             |        |     |              |       |   |        |   |        |

| SDO(IC1)/SDI(IC2) |                               | 0x0000  | )    | 1  | 1       | 0x00        | 0x00        | 0      |     | 0x0B0        | 00    |   | 0xCCXX |   |        |

|                   |                               |         |      |    |         |             |             |        |     |              |       |   |        |   |        |

| SDO(IC2)/SDI(IC3) |                               | 0x0000  | )    |    |         | 0x0000      |             | 1      | 1   | 0x00         | 0x00  | 0 | 0x0B00 | ) | 0xCCXX |

To unlock write brightness code (register 0x20~0xDF) register operation, write data 0xXXAA to register 0x0B00.

Device Address Field (16bits) Register Address Field (16bits)

| SDI(IC1)          | 1 1 | 0x00    | 0x00 | 0   | 0x0B0  | 00   |   |   | 0xXXAA |      |   |        |        |

|-------------------|-----|---------|------|-----|--------|------|---|---|--------|------|---|--------|--------|

|                   | B S | DevAddr |      | RW  | RegAd  | ldr  |   |   | Data   |      |   |        |        |

|                   |     |         |      |     |        |      |   |   |        |      |   |        |        |

| SDO(IC1)/SDI(IC2) |     | 0x0000  | )    | 1 1 | 0x00   | 0x00 | 0 |   | 0x0B0  | 00   |   | 0xXXAA | ]      |

|                   |     |         |      |     |        |      |   |   |        |      |   |        |        |

| SDO(IC2)/SDI(IC3) |     | 0x0000  | )    |     | 0x0000 |      | 1 | 1 | 0x00   | 0x00 | 0 | 0x0B00 | 0xXXAA |

Data Field (16bits)

To lock write configuration 1~16 (register 0x0~0xF) and mask code (Register 0x401~0x403) register operation, write data 0xAAXX to register 0x0B00.

To lock write brightness code (register 0x20~0xDF) register operation, write data 0xXXCC to register 0x0B00.

|                  | Device Address Field (16bits) | Register Address F | ield (16bits) |   | Data Field (16 | bits) |   |        |        |

|------------------|-------------------------------|--------------------|---------------|---|----------------|-------|---|--------|--------|

| SDI(IC1)         | 1 1 0x00 0x00                 | 0 0x0E             | 00            |   | 0xXXCC         | ,     | ] |        |        |

|                  | B S DevAddr                   | RW RegA            | ddr           |   | Data           |       |   |        |        |

|                  |                               |                    |               |   |                |       |   |        |        |

| SDO(IC1)/SDI(IC2 | 2) 0x0000                     | 1 1 0x00           | 0x00          | 0 | 0x0B0          | 00    |   | 0xXXCC | 7      |

| , , ,            |                               |                    |               |   |                |       | • |        | _      |

|                  |                               |                    |               |   |                |       |   |        |        |

| SDO(IC2)/SDI(IC3 | 0x0000                        | 0x0000             | )             | 1 | 1 0x00         | 0x00  | 0 | 0x0B00 | 0xXXCC |

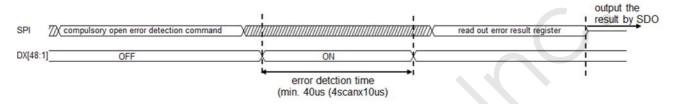

#### ■ Compulsory open error detection

|          | De | evice . | Address Field | d (16bits) | Reg | ister Address Field (16bits) | Data Field (16bits) |

|----------|----|---------|---------------|------------|-----|------------------------------|---------------------|

| SDI(IC1) | 1  | 1       | 0x00          | 0x00       | 0   | 0x0D00                       | 0x0001              |

|          | В  | S       | DevAddr       |            | RW  | RegAddr                      | Data                |

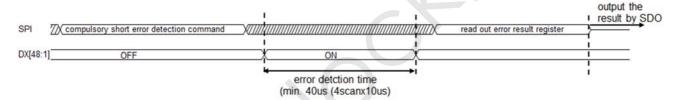

#### ■ Compulsory short error detection

|          | De | vice / | Address Field | d (16bits) | Reg | ister Address Field (16bits) | Data Field (16bits) |

|----------|----|--------|---------------|------------|-----|------------------------------|---------------------|

| SDI(IC1) | 1  | 1      | 0x00          | 0x00       | 0   | 0x0D01                       | 0x0001              |

|          | В  | S      | DevAddr       |            | RW  | RegAddr                      | Data                |

#### ■ Read open/short error detection result

| •                 |                                                                                                  |                                                  |                                                                               | 7 |                  |                                                                                                                                                                         |

|-------------------|--------------------------------------------------------------------------------------------------|--------------------------------------------------|-------------------------------------------------------------------------------|---|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                   | Device Address Field (16bits)                                                                    | <del>                                     </del> | ddress Field (16bits)                                                         | - |                  |                                                                                                                                                                         |

| SDI(IC1)          | 0 1 0x01 0x00                                                                                    | 1                                                | 0x0D03                                                                        |   | 0x0000           | 0x0000                                                                                                                                                                  |

|                   | B S DevAddr                                                                                      | RW                                               | RegAddr                                                                       |   |                  |                                                                                                                                                                         |

| SDO(IC1)          | 0x0000                                                                                           | 0 1                                              | 0x01 0x00                                                                     | 1 | 0x0D03           | N                                                                                                                                                                       |

| , ,               |                                                                                                  |                                                  |                                                                               |   |                  | read data from SCAN1<br>open/short error detection result<br>of Channel48~Channel33)                                                                                    |

|                   | Device Address Field (16bits)                                                                    | <del>                                     </del> | ddress Field (16bits)                                                         |   |                  |                                                                                                                                                                         |

| SDI(IC1)          | 0 1 0x01 0x00                                                                                    | 1                                                | 0x0D04                                                                        |   | 0x0000           | 0x0000                                                                                                                                                                  |

|                   | B S DevAddr                                                                                      | RW                                               | RegAddr                                                                       |   |                  |                                                                                                                                                                         |

| SDO(IC1)          | 0x0000                                                                                           | 0 1                                              | 0x01 0x00                                                                     | 1 | 0x0D04           | N                                                                                                                                                                       |

|                   |                                                                                                  |                                                  |                                                                               | - |                  | read data from SCAN1<br>open/short error detection result<br>of Channel32~Channel17)                                                                                    |

|                   | Device Address Field (16bits)                                                                    |                                                  | ddress Field (16bits)                                                         |   |                  |                                                                                                                                                                         |

| SDI(IC1)          | 0 1 0x01 0x00                                                                                    | 1                                                | 0x0D05                                                                        |   | 0x0000           | 0x0000                                                                                                                                                                  |

|                   | B S DevAddr                                                                                      | RW                                               | RegAddr                                                                       |   |                  |                                                                                                                                                                         |

|                   |                                                                                                  |                                                  |                                                                               |   |                  |                                                                                                                                                                         |

| SDO(IC1)          | 0x0000                                                                                           | 0 1                                              | 0x01 0x00                                                                     | 1 | 0x0D05           | N                                                                                                                                                                       |

| SDO(IC1)          | 0x0000                                                                                           | 0 1                                              | 0x01 0x00                                                                     | 1 | 0x0D05           | N read data from SCAN1 open/short error detection result of Channel16~Channel1)                                                                                         |

| SDO(IC1)          | 0x0000  Device Address Field (16bits)                                                            |                                                  |                                                                               | 1 | 0x0D05           | read data from SCAN1 open/short error detection result                                                                                                                  |

| SDO(IC1) SDI(IC1) | 20                                                                                               |                                                  | 0x01 0x00  ddress Field (16bits) 0x0D06                                       | 1 | 0x0D05           | read data from SCAN1 open/short error detection result                                                                                                                  |

|                   | Device Address Field (16bits)                                                                    | Register A                                       | ddress Field (16bits)                                                         | 1 |                  | read data from SCAN1<br>open/short error detection result<br>of Channel16~Channel1)                                                                                     |

|                   | Device Address Field (16bits) 0 1 0x01 0x00                                                      | Register A                                       | ddress Field (16bits)<br>0x0D06                                               | 1 |                  | read data from SCAN1<br>open/short error detection result<br>of Channel16~Channel1)                                                                                     |

| SDI(IC1)          | Device Address Field (16bits) 0 1 0x01 0x00 B S DevAddr                                          | Register A                                       | ddress Field (16bits)<br>0x0D06<br>RegAddr                                    |   | 0x0000           | read data from SCAN1 open/short error detection result of Channel16~Channel1)  0x0000                                                                                   |

| SDI(IC1) SDO(IC1) | Device Address Field (16bits)  0 1 0x01 0x00  B S DevAddr  0x0000  Device Address Field (16bits) | Register A                                       | ddress Field (16bits) 0x0D06 RegAddr 0x01 0x00                                |   | 0x0000<br>0x0D06 | read data from SCAN1 open/short error detection result of Channel16~Channel1)  Ox0000  N read data from SCAN2 open/short error detection result of Channel48~Channel33) |

| SDI(IC1)          | Device Address Field (16bits)  0                                                                 | Register A                                       | ddress Field (16bits) 0x0D06 RegAddr  0x01 0x00  ddress Field (16bits) 0x0D07 |   | 0x0000           | read data from SCAN1 open/short error detection result of Channel16~Channel1)  0x0000  N read data from SCAN2 open/short error detection result                         |

| SDI(IC1) SDO(IC1) | Device Address Field (16bits)  0 1 0x01 0x00  B S DevAddr  0x0000  Device Address Field (16bits) | Register A                                       | ddress Field (16bits) 0x0D06 RegAddr 0x01 0x00                                |   | 0x0000<br>0x0D06 | read data from SCAN1 open/short error detection result of Channel16~Channel1)  Ox0000  N read data from SCAN2 open/short error detection result of Channel48~Channel33) |

| SDI(IC1) SDO(IC1) | Device Address Field (16bits)  0                                                                 | Register A                                       | ddress Field (16bits) 0x0D06 RegAddr  0x01 0x00  ddress Field (16bits) 0x0D07 |   | 0x0000<br>0x0D06 | read data from SCAN1 open/short error detection result of Channel16~Channel1)  Ox0000  N read data from SCAN2 open/short error detection result of Channel48~Channel33) |

read data from SCAN2 open/short error detection result of Channel32~Channel17)

### 48-Channel Low Voltage High Constant Current LED <u>Driver with 1:4 Time-Multiplexing</u>

|          | De | evice | Address Field | d (16bits) | Reg | ister Add | dress Field | (16bits) |   |        |        |

|----------|----|-------|---------------|------------|-----|-----------|-------------|----------|---|--------|--------|

| SDI(IC1) | 0  | 1     | 0x01          | 0x00       | 1   |           | 0x0D08      |          |   | 0x0000 | 0x0000 |

|          | В  | S     | DevAddr       |            | RW  |           | RegAdd      | r        |   |        |        |

|          |    |       |               |            |     |           |             |          |   |        |        |

| SDO(IC1) |    |       | 0x0000        |            | 0   | 1         | 0x01        | 0x00     | 1 | 0x0D08 | N      |

read data from SCAN2 open/short error detection result of Channel16~Channel1)

The register 0xD09~0xD0B for the open/short error detection result of SCAN3 of channel48~channel1.

The register 0xD0C~0xD0E for the open/short error detection result of SCAN4 of channel48~channel1.

#### Software reset command

|          | De | evice . | Address Field | d (16bits) | Reg | ister Address Field (16bits) | Data Field (16bits) |

|----------|----|---------|---------------|------------|-----|------------------------------|---------------------|

| SDI(IC1) | 0  | 1       | 0x01          | 0x00       | 0   | 0x0E00                       | 0x0001              |

|          | В  | S       | DevAddr       |            | RW  | RegAddr                      | Data                |

#### ■ Fault reset command

|          | De | evice | Address Field | d (16bits) | Reg | ister Address Field (16bits) | Data Field (16bits) |

|----------|----|-------|---------------|------------|-----|------------------------------|---------------------|

| SDI(IC1) | 1  | 1     | 0x00          | 0x00       | 0   | 0x0E33                       | 0x55AA              |

|          | B  | S     | DevAddr       |            | RW  | RegAddr                      | Data                |

#### ■ Open/Short Error Detection Operation

For the open or short error detection, enable the configuration9 register bit 14 or bit 13. MBI6353 will perform error detection after the "compulsory open/short error detection command". The result of error detection will be stored on open/short error result (register 0xD03~0xD0E) register after the operation of SCAN1 to SCAN4 is done. The error report will be pushed out after the read out error result register command. MBI6353 shift out MSB of error reports to LSB of error reports from SDO simultaneously.

#### Compulsory open error detection

#### Compulsory short error detection

# Register Maps

| ADDRESS     | REGISTER NAME                                                                          | R/W      |

|-------------|----------------------------------------------------------------------------------------|----------|

| 0x0         | Configuration1 register                                                                | R/W      |

| 0x1         | Configuration2 register                                                                | R/W      |

| 0x2         | Configuration3 register                                                                | R/W      |

| 0x3         | Configuration4 register                                                                | R/W      |

| 0x4         | Configuration5 register                                                                | R/W      |

| 0x5         | Configuration6 register                                                                | R/W      |

| 0x6         | Configuration7 register                                                                | R/W      |

| 0x7         | Configuration8 register                                                                | R/W      |

| 0x8         | Configuration9 register                                                                | R/W      |

| 0x9         | Configuration10 register                                                               | R/W      |

| 0xA         | Configuration11 register                                                               | R/W      |

| 0xB         | Configuration12 register                                                               | R/W      |

| 0xC         | Configuration13 register                                                               | R/W      |

| 0xD         | Configuration14 register                                                               | R/W      |

| 0xE         | Configuration15 register                                                               | R        |

| 0xF         | Configuration16 register                                                               | R/W      |

| 0x10~0x1F   | RESERVE                                                                                | <u> </u> |

| 0x20~0x4F   | SCAN1 brightness code of Channel48~Channel1                                            | W        |

| 0x50~0x7F   | SCAN2 brightness code of Channel48~Channel1                                            | W        |

| 0x80~0xAF   | SCAN3 brightness code of Channel48~Channel1                                            | W        |

| 0xB0~0xDF   | SCAN4 brightness code of Channel48~Channel1                                            | W        |

| 0xE0~0x3FE  | RESERVE                                                                                | -        |

| 0x3FF       | Fault status register                                                                  | R        |

| 0x401       | Channel mask1 code of Channel48~Channel33                                              | R/W      |

| 0x402       | Channel mask2 code of Channel32~Channel17                                              | R/W      |

| 0x403       | Channel mask3 code of Channel16~Channel1                                               | R/W      |

| 0x404~0xAFF | RESERVE                                                                                | -        |

| 0xB00       | Lock/Unlock register                                                                   | R/W      |

| 0xB01~0xCFF | RESERVE                                                                                | -        |

| 0xD00       | Compulsory open error detection command                                                | W        |

| 0xD01       | Compulsory short error detection command                                               | W        |

| 0xD03       | Open/Short error result register (SCAN1 error detection result of Channel48~Channel33) | R        |

| 0xD04       | Open/Short error result register (SCAN1 error detection result of Channel32~Channel17) | R        |

| 0xD05       | Open/Short error result register (SCAN1 error detection result of Channel16~Channel1)  | R        |

| 0xD06       | Open/Short error result register (SCAN2 error detection result of Channel48~Channel33) | R        |

| 0xD07       | Open/Short error result register (SCAN2 error detection result of Channel32~Channel17) | R        |

| 0xD08       | Open/Short error result register (SCAN2 error detection result of Channel16~Channel1)  | R        |

| 0xD09       | Open/Short error result register (SCAN3 error detection result of Channel48~Channel33) | R        |

| 0xD0A       | Open/Short error result register (SCAN3 error detection result of Channel32~Channel17) | R        |

| 0xD0B       | Open/Short error result register (SCAN3 error detection result of Channel16~Channel1)  | R        |

| 0xD0C       | Open/Short error result register (SCAN4 error detection result of Channel48~Channel33) | R |

|-------------|----------------------------------------------------------------------------------------|---|

| 0XD0D       | Open/Short error result register (SCAN4 error detection result of Channel32~Channel17) | R |

| 0xD0E       | Open/Short error result register (SCAN4 error detection result of Channel16~Channel1)  | R |

| 0xD0F~0xD56 | RESERVE                                                                                | - |

| 0xE00       | Software reset command                                                                 | W |

| 0xE33       | Fault reset command                                                                    | W |

MBI6353

# 48-Channel Low Voltage High Constant Current LED Driver with 1:4 Time-Multiplexing

# **Definition of Configuration 1 Register**

| MSB |    |    |    |    |    |   |   |   |   |   |   |   |   |   | LSB |  |

|-----|----|----|----|----|----|---|---|---|---|---|---|---|---|---|-----|--|

| 15  | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0   |  |

|    |    |    |    |    |    | SF | I ADDI | RESS:0 | )x0 |   |   |   |   |   |   |

|----|----|----|----|----|----|----|--------|--------|-----|---|---|---|---|---|---|

| 15 | 14 | 13 | 12 | 11 | 10 | 9  | 8      | 7      | 6   | 5 | 4 | 3 | 2 | 1 | 0 |

| 0  | 0  | 0  | 0  | 1  | 1  | 0  | 0      | 0      | 0   | 0 | 1 | 0 | 0 | 0 | 0 |

| Bit   | Attribute  | Definition                              | Default<br>Value | Function                                                                                                                                                                                                                                                                                                                                                                              |

|-------|------------|-----------------------------------------|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15:12 | Read/Write | RESERVE                                 | 0000             | -                                                                                                                                                                                                                                                                                                                                                                                     |

| 11:10 | Read/Write | Global current<br>division<br>(GCG1)    | 11               | Mode change for output current lout 00: Mode= 1/8 01: Mode= 1/4 10: Mode= 1/2 11: Mode= 1/1                                                                                                                                                                                                                                                                                           |

| 9:8   | Read/Write | Number of scrambles                     | 00               | 00: 1 scramble 01: 8 scrambles 10: 16 scrambles 11: 32 scrambles                                                                                                                                                                                                                                                                                                                      |

| 7     | Read/Write | RESERVE                                 | 0                | -                                                                                                                                                                                                                                                                                                                                                                                     |

| 6:5   | Read/Write | Number of scans                         | 00               | 00: 1 scan<br>01: 2 scans<br>10: 3 scans<br>11: 4 scans                                                                                                                                                                                                                                                                                                                               |

| 4     | Read/Write | Display mode                            | 1                | 0: continue mode,<br>1: one shot mode                                                                                                                                                                                                                                                                                                                                                 |

| 3:0   | Read/Write | Hybrid(PWM/PAM)<br>brightness threshold | 0000             | 0000: PWM mode only 0001: 4 0010: 8 0011: 16 0100: 32 0101: 64 0110: 128 0111: 256 1000: 512 1001: 1024 1010 ~ 1110: not used(same as code '0000') 1111: PAM mode only (10-bit brightness code only) Note: If mode change is 2'b00, don't use HBT greater than 128. If mode change is 2'b01, don't use HBT greater than 256. If mode change is 2'b10, don't use HBT greater than 512. |

# 48-Channel Low Voltage High Constant Current LED Driver with 1:4 Time-Multiplexing